# CI1301 Datasheet

# **High Performance Automatic Speech Recognition processor**

## SSOP24

Length: 8.6mm Width: 6.0mm

Thickness: 1.64mm

# Brain Neural Network Processing Unit • GPIO (BNPU) – 10 fa

– BNPU V3 support DNN \ TDNN \ RNN \ CNN and other neural networks and parallel vector operations. It can realize speech recognition, voiceprint recognition, command word self-learning, voice detection, deep learning noise reduction and other functions

#### CPU and Storage

- CPU frequency up to 220 MHz

- 1MBytes of Flash memory inside

- 640K Bytes of SRAM inside

- 512bit eFuse for encryption

#### Audio Codec

- High performance, Low-power consumption audio

ADC with SNR ≥ 95dB

- Low-power consumption audio DAC with SNR ≥ 95dB

#### Audio interfaces

- One IIS interface, master/slave configurable

- One Dual-channel PDM interface

#### ADC and PWM

- One channel 12bit SAR ADC

- Six PWM interfaces

- 10 fast GPIOs, response speed up to 20MHz

- 7 GPIOS with 5V input tolerant capability

## • Reset and power management

- Build-in PMU

- PMU input voltage range: 3.6V to 5.5V

- Power-on Reset (POR)

- Power Voltage Detector (PVD)

#### Clock management

Built in RC oscillator, also support external crystal oscillator. Developers can choose to use built-in RC or external crystal as chip clock source according to different applications

## • Communication interface

- One IIC interface

- Three UART interfaces with 3M baud rate

#### Timer and Watch dog

- Four 32-bit timers, Two watch dogs

# **Contents**

| 1 | Descr  | ription                               | 3  |

|---|--------|---------------------------------------|----|

|   | 1.1    | Functional overview                   | 3  |

|   | 1.2    | Chip Specifications                   | 4  |

| 2 | Pin D  | riagram and Function Description      | 6  |

|   | 2.1    | Pin Diagram                           | 6  |

|   | 2.2    | Pin descriptions                      | 7  |

|   | 2.3    | Alternate functions                   | 9  |

| 3 | Electr | rical Characteristics                 | 10 |

| 4 | Packa  | aging Information                     | 12 |

| 5 | Order  | · Information                         | 13 |

| 6 | Appli  | cation                                | 14 |

|   | 6.1    | Application Reference Circuit Diagram | 14 |

|   | 6.2    | Other Application Notices             | 15 |

# 1 Description

#### 1.1 Functional overview

CI1301 is a high-performance artificial intelligence chip for speech recognition and processing.

CI1301 integrates brain neural network processor BNPU V3.0 developed by chipintelli, 220Mhz

CPU, up to 640k Byte RAM, integrated PMU, integrated RC oscillator, integrated dual channel high-performance low-power consumption audio codec, integrated multiple UART, IIC, IIS, PWM, GPIO, PDM and other peripheral control interfaces, only need a few peripheral device for internal LDO. It has high cost performance.

CI1301 uses industrial design standards and has high environmental reliability. The working temperature range of the chip is between - 40°C and + 85°C. It complies with MSL3 humidity sensitivity level, 4KV contact discharge test standard of IEC 61000-4-2, FCC electromagnetic compatibility standard and ROHS and REACH environmental protection standards.

CI1301 support the 3rd generation BPNU technology of Chipintelli, which can support support DNN \ TDNN \ RNN \ CNN and other neural networks and parallel vector operations. It can realize speech recognition, voiceprint recognition, command word self-learning, voice detection, deep learning noise reduction and other functions. It also support Chinese, English, Japanese and other global languages.

CI1301 can be widely used by home appliances, lighting, toys, wearable devices, industry, automobile and other product fields to realize voice interaction and control, and the application of various intelligent voice solutions It can implement the requirements of improving efficiency and reducing cost for the existing intelligent speech off-line recognition application. Due to the flash capacity, the chip only supports small acoustic models, and only supports less than 100 command words in normal household scenes with moderate noise. If the application scheme requires more command words, please use CI1302 or CI1303.

# 1.2 Chip Specifications

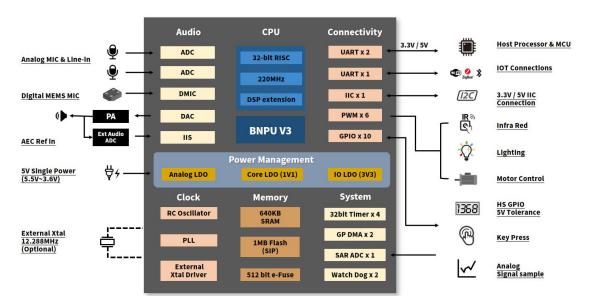

The functional block diagram of CI1301 chip is shown in the figure below:

Diagram 1-1 Function Block Diagram

#### ■ Brain Neural Network Processing Unit (BNPU)

- BNPU V3 support support DNN \ TDNN \ RNN \ CNN and other neural networks and parallel vector operations. It can realize speech recognition, voiceprint recognition, command word self-learning, voice detection, deep learning noise reduction and other functions

#### ■ CPU

- 32 bit high performance CPU, frequency up to 220MHz

- 32 bit signal-period multiplier, support DSP accelerate

#### **■** Storage

- 640KB SRAM inside

- 512bit e-Fuse inside

- 1MB Flash inside

#### **■** Audio Interface

- High performance, Low consumption audio codec module, support double ADC sampling and signal DAC playing

- Support automatic level control (ALC)

- Support 8kHz/16kHz/24kHz/32kHz/44.1kHz/48kHz Sampling rate

- Support one IIS audio extended path

- Support one PDM interface, it can support one or two digital MEMS microphone

#### ■ PMU

- Three LDOs inside, the chip only need a few peripheral device for internal LDOs. External power chip is not necessary

- 5V Power supply, the power supply range supports a minimum of 3.6V input and a maximum of 5.5V input

#### ■ CLOCK

- Built in RC oscillator, also support external crystal oscillator. Developers can choose to use built-in RC or external crystal as chip clock source according to different applications

#### ■ SAR ADC

- Support one input channel of 12bit SAR ADC with 1MHz sampling rate

- Support ADC IO and GPIO multiplexing

#### ■ Peripheral Interface and Timer

- Three UART interfaces with 3M baud rate maximum

- One IIC interface, support IIC extended device

- Six PWM interfaces, support direct driving for light control and motor applications

- Four 32-bit timers inside

- Built-in one independent watchdog (IWDG)

- Built-in one window watchdog (WWDG)

#### ■ GPIO

- Support 10 GPIOS

- Some GPIOS with 5V tolerant capability

- Each GPIO can be configurable for interruption and support pull up and pull down setting

#### **■** Development Support

- Provide software development package, application examples and notices

- Content and services can be realized online, address: https://aiplatform.chipintelli.com

## **■** Firmware burning and protection

- Support firmware upgrade by UART and firmware protection

#### **■** EMC and ESD

- Excellent EMC design and support FCC standard

- Excellent ESD design, it can pass 4KV contact discharge test

## ■ ROHS and REACH

- Support ROHS and REACH standards

## ■ Packaging and Operating temperature

- Devices Packaging: SSOP24, Length\*Width\*Thickness = 8.6\*6.0\*1.64 mm

- Operating temperature: -40°C~+85°C

# 2 Pin Diagram and Function Description

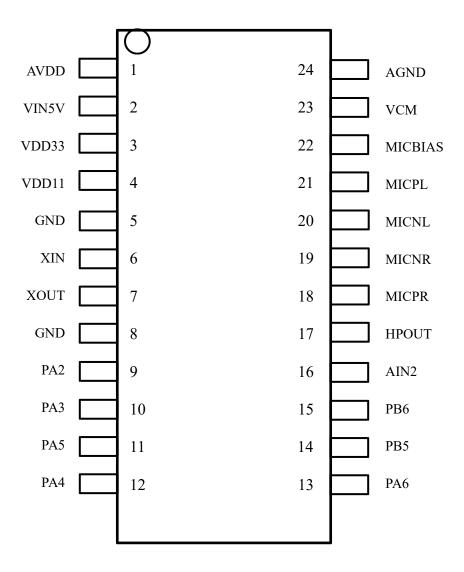

# 2.1 Pin Diagram

V1.2

# 2.2 Pin descriptions

Table 2-1 Pin Descriptions

| Pin number | Pin Name | Туре | 5V<br>Tolerant | Power on default state | <b>Description Alternate functions</b>                                                                                                                                                                                                                                                                                                   |

|------------|----------|------|----------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | AVDD     | P    | -              | -                      | 3.3V output or 3.3V analog power supply, output capacitance/input capacitance is 4.7uF                                                                                                                                                                                                                                                   |

| 2          | VIN5V    | P    | -              | -                      | VIN5V is the PMU power supply input pin. The normal working input voltage range is 3.6V-5.5V. A 4.7uf input capacitor is connected externally. The maximum input voltage of this pin is 6.5V. Note that over-voltage and surge protection devices need to be added, such as a TVS and a 4.7 ohm resistor to protect against surge impact |

| 3          | VDD33    | P    | -              | -                      | 3.3V output or 3.3V IO power supply, output capacitance/input capacitance is 4.7uF                                                                                                                                                                                                                                                       |

| 4          | VDD11    | P    | -              | -                      | 1.1V output or 1.1V Power supply, output capacitance/input capacitance is 4.7uF                                                                                                                                                                                                                                                          |

| 5          | GND      | P    | _              | _                      | Ground                                                                                                                                                                                                                                                                                                                                   |

| 6          | XIN      | I    | -              | -                      | XIN (external crystal and oscillator interface, initial state at startup, no external crystal oscillator is required for normal application)     GPIO PA0     PWM5                                                                                                                                                                       |

| 7          | XOUT     | О    | -              | -                      | XOUT (external crystal and oscillator interface, initial state at startup, no external crystal oscillator is required for normal application)     GPIO PA1                                                                                                                                                                               |

| 8          | GND      | P    | -              | -                      | Ground                                                                                                                                                                                                                                                                                                                                   |

| 9          | PA2      | Ю    | V              | IN,T+D                 | 1. GPIO PA2 (Initial state at startup) 2. IIS SDI 3. IIC SDA 4. UART1 TX 5. PWM0                                                                                                                                                                                                                                                         |

| 10         | PA3      | Ю    | V              | IN,T+D                 | <ol> <li>GPIO PA3 (Initial state at startup)</li> <li>IIS_LRCLK</li> <li>IIC_SCL</li> <li>UART1_RX1</li> <li>PWM1</li> </ol>                                                                                                                                                                                                             |

| 11         | PA5      | Ю    | V              | IN,T+D                 | <ol> <li>GPIO PA5 (Initial state at startup)</li> <li>IIS_SCLK</li> <li>PDM_DAT</li> <li>UART2_TX</li> <li>PWM3</li> </ol>                                                                                                                                                                                                               |

| 12         | PA4      | Ю    | V              | IN,T+U                 | 1. GPIO PA4 (Initial state at startup)/PG_EN (For software update, Note1) 2. IIS_SDO 3. PWM2                                                                                                                                                                                                                                             |

| 13         | PA6      | Ю    | V              | IN,T+D                 | <ol> <li>GPIO PA6 (Initial state at startup)</li> <li>IIS_MCLK</li> <li>PDM_CLK</li> <li>UART2_RX</li> </ol>                                                                                                                                                                                                                             |

|    |         |   |          |        | 5. PWM4                                                                                                                  |  |  |

|----|---------|---|----------|--------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| 14 | PB5     | Ю | <b>√</b> | IN,T+U | <ol> <li>GPIO PB5 (Initial state at startup)</li> <li>UART0 TX</li> <li>IIC SDA</li> <li>PWM1</li> </ol>                 |  |  |

| 15 | PB6     | Ю | <b>V</b> | IN,T+U | 1. GPIO PB6 (Initial state at startup) 2. UART0_RX 3. IIC_SCL 4. PWM2                                                    |  |  |

| 16 | AIN2    | Ю | -        | IN,T+U | <ol> <li>Reserved (Initial state at startup)</li> <li>GPIO PC4</li> <li>PWM0</li> <li>SAR ADC input channel 2</li> </ol> |  |  |

| 17 | HPOUT   | О | -        | -      | DAC output                                                                                                               |  |  |

| 18 | MICPR   | I | -        | -      | Right Microphone P input                                                                                                 |  |  |

| 19 | MICNR   | I | -        | -      | Right Microphone N input                                                                                                 |  |  |

| 20 | MICNL   | I | -        | -      | Left Microphone N input                                                                                                  |  |  |

| 21 | MICPL   | I | -        | -      | Left Microphone P input                                                                                                  |  |  |

| 22 | MICBIAS | О | -        | -      | Microphone Bias output                                                                                                   |  |  |

| 23 | VCM     | О | -        | -      | VCM Output                                                                                                               |  |  |

| 24 | AGND    | P | -        | _      | Analog ground                                                                                                            |  |  |

#### Conformity with definition:

- I input

- O output

- IO bidirectional

- P power or ground

- T+D Tristate plus pull-down

- T+U Tristate plus pull-up

- OUT power-on defaults to output mode

- IN power-on defaults to input mode

The driving capability of all GPIOs can be configured, and the pull up and pull down resistance can be configured by software.

Note1: At startup, the voltage of Pin PA4(PG\_EN) will be detected. When the voltage is high(higher than 2.0V), the chip can start serial port upgrade service and program. When the voltage is low(lower than 0.8V), the chip start directly from Flash as normal.

## 2.3 Alternate functions

Table 2-2 Alternate Functions

| Pin Name | Function1 | Function2 | Function3 | Function4 | Function5 | Analog<br>Function | Specific<br>Function |

|----------|-----------|-----------|-----------|-----------|-----------|--------------------|----------------------|

| XIN      | PA0       | PWM5      | -         | -         | -         | XIN                | -                    |

| XOUT     | PA1       | -         | -         | -         | -         | XOUT               | -                    |

| PA2      | PA2       | IIS_SDI   | IIC_SDA   | UART1_TX  | PWM0      | -                  | -                    |

| PA3      | PA3       | IIS_LRCLK | IIC_SCL   | UART1_RX  | PWM1      | -                  | -                    |

| PA4      | PA4       | IIS_SDO   | -         | -         | PWM2      | -                  | PG_EN<br>Note1       |

| PA5      | PA5       | IIS_SCLK  | PDM_DAT   | UART2_TX  | PWM3      | -                  | -                    |

| PA6      | PA6       | IIS_MCLK  | PDM_CLK   | UART2_RX  | PWM4      | -                  | -                    |

| PB5      | PB5       | UART0_TX  | IIC_SDA   | PWM1      | -         | -                  | -                    |

| PB6      | PB6       | UART0_RX  | IIC_SCL   | PWM2      | -         | -                  | -                    |

| AIN2     | -         | PC4       | -         | PWM0      | -         | AIN2               | -                    |

Note1: The 12 pin of this chip is PA4(PG\_EN). It is pulled up by default. When the power on is judged to be high, the chip can automatically enter the upgrade mode when it detects an upgrade signal on UART0 when it is powered on. At this time, the supporting upgrade tool can be used to program the flash inside the chip. If no upgrade signal is detected on UART0, it will enter the normal working mode.

# 3 Electrical Characteristics

Table 3-1 Electrical Characteristics Table

| Symbol                 | Description                                                                                                                                               | Min.      | Typical | Max.      | Unit |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-----------|------|

| VIN5V                  | PMU Power supply                                                                                                                                          | 3.6       | 5       | 5.5       | V    |

| AVDD                   | Analog Codec Power supply                                                                                                                                 | 2.97      | 3.3     | 3.63      | V    |

| VDD33                  | Chip IO Power Supply                                                                                                                                      | 2.97      | 3.3     | 3.63      | V    |

| VDD11                  | Chip core Power Supply<br>Voltage                                                                                                                         | 0.99      | 1.1     | 1.22      | V    |

| $ m V_{IH}$            | Input High Voltage, 3.0V ≤ VDD33 ≤ 3.6V                                                                                                                   | 0.7×VDD33 | -       | -         | V    |

| V <sub>IL</sub>        | Input Low Voltage, 3.0V ≤ VDD33 ≤ 3.6V                                                                                                                    | -         | -       | 0.3×VDD33 | V    |

| $ m V_{OL}$            | Output Low Voltage @I <sub>OL</sub> = 2,4mA                                                                                                               | -         | -       | 0.4       | V    |

| $V_{	ext{OH}}$         | Output High Voltage @I <sub>OH</sub> = 2,4mA                                                                                                              | 2.4       | -       | -         | V    |

| I5VIO                  | Driving current when IO (withstand 5V voltage) outputs 3.3V                                                                                               | 5         | 1       | 23        | mA   |

| I33VIO                 | Driving current when IO (withstand 3.3V voltage) outputs 3.3V                                                                                             | 12        | -       | 26        | mA   |

| ΣIVDD                  | Driving current of all GPIOs                                                                                                                              | -         | -       | 180       | mA   |

| Pde                    | 5V power supply, and the chip's VDD11 is powered by external DC-DC chip. The total power consumption of 5V input during normal identification at TA= 25°C | 70        | -       | 150       | mW   |

| Pdi                    | 5V power supply, and the chip uses internal PMU. The total power consumption of 5V input during normal identification at TA= 25°C                         | 145       | -       | 250       | mW   |

| RC                     | T <i>A</i> =-40 to 85°C                                                                                                                                   | -4        | -       | +3        | %    |

| Oscillator<br>Accuracy | T <i>A</i> =-20 to 85°C                                                                                                                                   | -3        | -       | +3        | %    |

| Note1                  | T <i>A</i> =-10 to 70°C                                                                                                                                   | -2.5      | -       | +2.5      | %    |

| T <i>A</i><br>Note2    | Working ambient temperature that the chip using external crystal oscillator can adapt to                                                                  | -40       | -       | +85       | °C   |

| Note3                  | Working ambient temperature that the chip using internal RC oscillator can adapt to                                                                       | -10       | -       | +70       | °C   |

| TST                    | Chip Storage temperature                                                                                                                                  | -55       | -       | +150      | °C   |

Note1: The RC oscillator built in the chip will produce a certain temperature drift with the change

of the ambient temperature. This temperature drift may affect the application requiring high-precision clock or the accuracy of serial communication with upper computer.

Note2: If the application requires a high-precision clock, or requires serial port communication and the ambient temperature range exceeds -10 to 70 °C, it is recommended to use an external crystal oscillator as the clock source, and the working ambient temperature can reach or exceed the industrial standard specifications. If the internal RC oscillator is used as the clock source, the baud rate of serial communication must be less than or equal to 115200bps. At the same time, the total deviation between the baud rate and the serial port of the upper computer shall not exceed 4% to ensure good communication. If the working environment temperature is - 10 to 70 °C, the baud rate deviation of the serial port of the upper computer must not exceed  $\pm$  1.5% in this temperature range. If the working environment temperature is - 20 to 85 °C, the baud rate deviation of the serial port of the upper computer must not exceed  $\pm$  1% in this temperature range.

Note3: When the upper computer is designed without crystal oscillator, the communication error should be minimized. Chipintelli can provide a self-adaptive scheme for baud rate of serial port, which needs to add a handshake command to the serial port protocol, and the upper computer ensures that it will reply according to the protocol requirements within 50ms after receiving the handshake command. After adding this self-adaptive scheme, the product can be used in applications where the working environment temperature is - 20 to 85 °C.

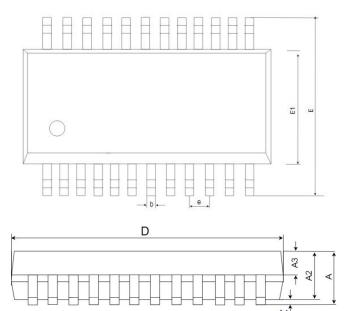

# 4 Packaging Information

#### COMMON DIMENSIONS

| COMMON DIMENSIONS |                  |      |      |  |  |  |  |  |

|-------------------|------------------|------|------|--|--|--|--|--|

| SYMBOL            | UNIT: MILLIMETER |      |      |  |  |  |  |  |

| 51111252          | MIN              | NOM  | MAX  |  |  |  |  |  |

| A                 | -                | _    | 1.75 |  |  |  |  |  |

| A1                | 0.10             | 0.15 | 0.25 |  |  |  |  |  |

| A2                | 1.30             | 1.48 | 1.50 |  |  |  |  |  |

| A3                | 0.6              | 0.65 | 0.70 |  |  |  |  |  |

| b                 | 0.23             | _    | 0.31 |  |  |  |  |  |

| С                 | 0.20             | _    | 0.24 |  |  |  |  |  |

| D                 | 8.55             | 8.6  | 8.75 |  |  |  |  |  |

| Е                 | 5.80             | 6.00 | 6.20 |  |  |  |  |  |

| E1                | 3.80             | 3.90 | 4.00 |  |  |  |  |  |

| e                 | 0.635BSC         |      |      |  |  |  |  |  |

| h                 | 0.30             | _    | 0.50 |  |  |  |  |  |

| L                 | 0.50             | -    | 0.80 |  |  |  |  |  |

| L1                | 1.05REF          |      |      |  |  |  |  |  |

| θ                 | 0                | _    | 8°   |  |  |  |  |  |

# 5 Order Information

Table 5-1 Order Information Table

| Orderable | Flash Status | Elech | Status      | Package | Pins      | Package         | Eco Plan              | MSL       | Op Temp |

|-----------|--------------|-------|-------------|---------|-----------|-----------------|-----------------------|-----------|---------|

| Device    |              | Type  | Pins        | Qty     | ECO FIAII | Peak Temp       | (°C)                  |           |         |

| CI1301    | 1MByte       | TBD   | SSOP24/Tube | 24      | 50        | RoHS &<br>Green | Level-3<br>260C-UNLIM | -40 to 85 |         |

# 6 Application

# 6.1 Application Reference Circuit Diagram

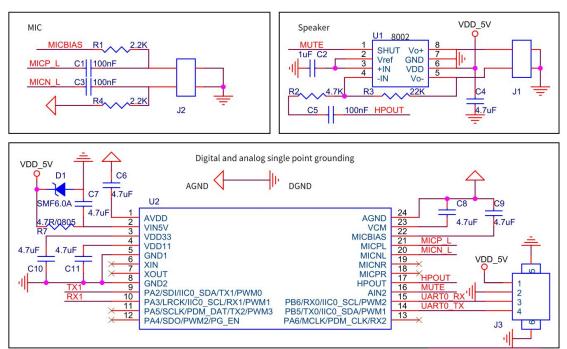

The periphery of CI1301 chip only needs a few devices to support all kinds of voice applications. The chip can support single microphone differential input or single microphone single ended input, and can also choose whether AEC echo cancellation function is required. Users can select the appropriate circuit according to the function, power consumption and cost requirements of the designed application scheme. The simplest application reference circuit diagram of the chip is described in detail below.

Diagram 6-1 The circuit diagram of the simplest CI1301's application scheme

The figure above is the circuit diagram of the simplest CI1301's application scheme, supporting single microphone differential input and power amplifier output. The chip can use 5V direct power supply, and users can design according to the corresponding peripheral device specifications in the figure above.

If the online upgrade function is to be considered in the schematic design, the UART0 pin can be led out, to facilitate the firmware upgrade of the flash inside the main chip through UART0. The PA4 (PG\_EN) pin of the chip is internally pulled up, and the power on defaults state is the upgrade mode. After power on, the chip detect the upgrade signal from the external UART0 port, and directly start the upgrade. The default startup time of the chip is about 850ms with extending due to the detection of upgrade mode. If the user has high requirements for the startup time, the PA4 pin can be led out, two  $2.2k\Omega$  pull-down resistors can be added to the ground, and a test point is

added in the middle of the two  $2.2k\Omega$  resistors. At this time, the chip's startup state is in the normal mode, and the startup time is about 350ms, which can shorten the startup time. If you want to upgrade online at this time, you can supply high level to the intermediate test points connected by two  $2.2k\Omega$  resistors externally, pull PA4 pin up, and then upgrade through UART0.

The chip scheme can choose differential microphone design or single ended microphone design. The differential microphone design in the figure above is recommended. If the user has requirements to reduce the cost, the microphone part in the figure above can be modified to the single ended microphone design, which can use less passive devices than the differential microphone. However, this method is only recommended to be used when the microphone line length is less than 20cm. Otherwise, because the line is too long and the anti-interference effect is not enough, the speech recognition effect is not as good as that of the differential microphone design. The power amplifier in the figure above adopts class AB power amplifier, and 8002 power amplifier chip is recommended. Users can also choose the power amplifier chip according to the requirements of the scheme. If the power amplifier function is not required, this part of the circuit can also be removed to reduce the cost. If users need AEC echo cancellation function, they can use a microphone input channel to connect the analog signal input of AEC.

If the user has no special requirements to reduce the power consumption, it is recommended to directly use the PMU inside the chip for power supply. If there are requirements to reduce the power consumption, an external DCDC chip can be added to supply power to the chip at 1.1V to reduce power consumption. The UART ports of the chip support 5V communication. The UART0 port in the figure above is connected with a 3.3V signal. If 5V is to be connected, add a pull-up resistance connected to 5V around the RX and TX pins of UART0 without adding an additional voltage conversion circuit.

# **6.2** Other Application Notices

- 1. Due to the principle of semiconductor technology, the RC oscillator built in the chip will produce a certain temperature drift in high and low temperature environments. If the operating temperature range of the user's application is 40 to 85 °C, it is recommended to use an external crystal oscillator in the circuit scheme. In addition, if high-precision PWM output (frequency accuracy error less than  $\pm$  2%) or high-speed serial communication (baud rate greater than 115200bps) is required in the application, it is also recommended to use external crystal oscillator.

- 2. If the operating temperature of the application is in the range of -10 to 70 °C, and only low-speed serial port communication is conducted with the upper computer (baud rate is less than or equal to 115200bps), this kind of circuit scheme can directly use the RC oscillator built in the chip(the frequency deviation of upper computer must be equal to or less than  $\pm$  1.5%). When the

upper computer is designed without crystal oscillator, the communication error should be minimized. Chipintelli can provide a self-adaptive scheme for baud rate of serial port, which needs to add a handshake command to the serial port protocol, and the upper computer ensures that it will reply according to the protocol requirements within 50ms after receiving the handshake command. After adding this self-adaptive scheme, the product can be used in applications where the working environment temperature is - 20 to 85 °C.

- 3. If the application does not require the frequency accuracy of the RC oscillator, the RC oscillator built in the chip can be used.

- 4.The PMU in the chip include three LDOs, The LDOs provide 3.3V and 1.1V for chip Operating. In general, external power chips for 3.3V and 1.1V Power supply is not necessary. The ripple of external 5V power supply shall be less than 300mV.

- 5. The chip is lead-free. When SMT soldering, please set parameters such as furnace temperature and time according to lead-free standard.

- 6. We should pay attention to the electrostatic effect when we use and pack chips. It is suggested that antistatic materials be used for isolation.

- 7. Due to the flash capacity, CI1301 only supports small acoustic models, and only supports less than 50 command words. If the application requires more command words, please use CI1302 or CI1303.

- Chipintelli reserves the right to change the instruction without further notice. Customers should obtain the latest version before placing an order, and verify that the relevant information is complete and up-to-date.

- Under specific conditions, any semiconductor product has a certain possibility of failure or failure. The buyer has the responsibility to comply with safety standards and take safety measures when using the product for system design and manufacturing, to avoid potential failure risk which may cause personal injury or property loss.

- Product improvement is endless. Chipintelli will provide customers with better products wholeheartedly!