### CI2312 Datasheet

### High Performance AI Speech BLE Chip

### TSSOP24

Length:7.8mm Width:6.4mm Thickness:1.2mm

### • Brain Neural Network Processing Unit (BNPU)

BNPU V3 support DNN \ TDNN \ RNN \

CNN and other neural networks and parallel

vector operations. It can realize speech

recognition, voiceprint recognition, command

word self-learning, voice detection, deep

learning noise reduction and other functions

#### • CPU and Storage

- CPU frequency up to 240 MHz

- 1 MBytes of Flash memory inside

- Built-in 640KBytes SRAM

- Built-in 512bit eFuse for application encryption

- Audio Codec

- High performance low power audio ADC,  $SNR \ge 95dB$

- Low-power audio DAC,  $SNR \ge 95 dB$

- Audio interfaces

- One Dual-channel PDM interface

- ADC and PWM

- Two channel 12bit SAR ADC

- Three PWM interfaces

- GPIO

ChipIntelli C12312

- Reset and power management

- Build-in PMU

- PMU input voltage range: 3.6V to 5.5V

- Power-on Reset (POR)

- Power Voltage Detector (PVD)

- Clock

- -16MHz external crystal oscillator

- Communication interface

- One IIC interface

- Two UART interfaces, supporting 5V

- communication and maximum 3Mbps rate

- Timer and Watch dog

- Four 32-bit timers, Two watch dogs

- Wireless

- GFSK modulation mode, 1Mbps mode of receiving sensitivity up to -90dbm

- Maximum transmit output power up to

+8dBm

- Supports BLE broadcasting

- Fast channel switching, multi-channel frequency modulation algorithm can be realized

- Seven high-speed GPIOs with response rates

up to 20MHz

- Five of the GPIOs support 5V input

# Catalogue

| 1 Description                                        |

|------------------------------------------------------|

| 1.1 Functional overview4                             |

| 1.2 Chip Specifications                              |

| 2 Pin Diagram and Function Description               |

| 2.1 Pin Diagram                                      |

| 2.2 Pin descriptions                                 |

| 2.3 Alternate functions                              |

| 3 Electrical Characteristics                         |

| 4 Wireless characteristics                           |

| 5 Packaging Information14                            |

| 6 Order Information                                  |

| 7 Application错误!未定义书签。                               |

| 7.1 Application Reference Circuit Diagram 错误! 未定义书签。 |

| 7.2 Other Application Notices                        |

# **1** Description

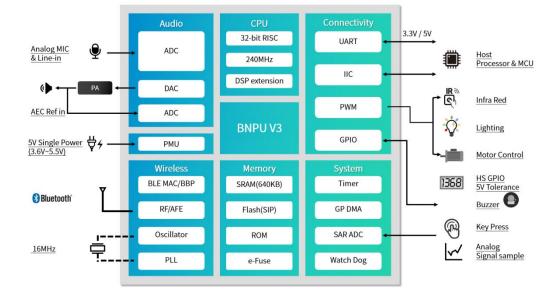

#### **1.1** Functional overview

CI2312 is a new generation of high-performance neural network intelligent speech chip developed by Chipintelli. It integrates the brain neural network processor BNPU V3 and CPU core developed by Chipintelli. The system frequency can reach 240MHz, the built-in SRAM is up to 640KByte, and the integrated PMU power management unit. Integrated dual-channel high-performance low-power Audio Codec and multi-channel UART, IIC, PWM, GPIO, PDM and other peripheral control interfaces, integrated 2.400~2.483GHz universal ISM band wireless transceiver chip, embedded baseband communication protocol. The chip only needs a small number of peripheral devices such as resistors and capacitors to realize various intelligent voice product hardware solutions, which is a low-cost wireless system solution.

CI2312 uses industrial design standards, with high environmental reliability, chip operating temperature range between -40°C to +85°C, in line with MSL3 humidity sensitivity level, in line with IEC 61000-4-2 4KV contact discharge test standards, in line with FCC electromagnetic compatibility standards, Comply with ROHS and REACH environmental standards.

CI2312 adopts the 3-generation BNPU technology of Chipintelli, which supports DNN\TDNN\RNN\CNN and other neural networks and parallel vector operations, and can realize the functions of speech recognition, voice print recognition, command word self-learning, speech detection and deep learning noise reduction, with strong echo cancellation and environmental noise suppression ability. The chip solution also supports Chinese, English, Japanese and other global languages, and can be widely used in household appliances, lighting, toys, wearable devices, industrial, automotive and other product fields to achieve voice interaction and control and various intelligent voice solution applications.

4

# 1.2 Chip Specifications

CI2312 chip function block diagram is shown as follows:

Figure 1-1 Block diagram of the chip functions

#### Wireless features

- Transmission mode (0dBm) working current 17mA; Receiving mode working current 18mA; Shutdown current 2uA.

- High performance RF design adopts GFSK modulation mode, and the receiving sensitivity of 1Mbps mode can reach -90dbm; Maximum output power +8dBm

- Supports BLE broadcasting

- Fast channel switching, can achieve multi-channel frequency modulation algorithm

#### **Brain Neural Network Processing Unit (BNPU)**

- BNPU V3 support DNN \ TDNN \ RNN \ CNN and other neural networks and parallel vector operations. It can realize speech recognition, voiceprint recognition, command word self-learning, voice detection, deep learning noise reduction and other functions

- CPU

- 32-bit high-performance CPU with a maximum operating frequency of 240MHz

- 32-bit single-period multiplier, supporting DSP expansion acceleration

■ Storage

- Built-in 640KB SRAM

- Built-in 512bit eFuse

- Built-in 2MB Flash

#### Audio interface

- Built-in high performance low power Audio Codec module, support dual-channel ADC sampling and single-channel DAC playback

- Supports Automatic Level Control (ALC)

- support 8 kHz / 16 kHz / 24 kHz / 32 kHz, 44.1 kHz, 48 kHz sampling rate

- Supports one PDM interface for connecting to one or two digital MEMS microphones

#### ■ Power management unit PMU

- Built-in 3 high-performance Ldos, no need to add a power chip, only a small amount of peripheral resistance container

- Support 5V power supply direct input, the minimum power supply range supports 3.6V input, the maximum power supply range supports 5.5V input

Clock

-16MHz external crystal oscillator

#### ■ SAR ADC

- 2 12bit SAR ADC input channels, sampling frequency up to 1MHz

- Peripherals and timers

- Two UART ports, supporting a maximum of 3 baud rate

- 1 IIC interface, which can be expanded by external IIC devices

- 3-channel PWM interface, light control and motor applications can be driven directly

- Built-in four groups of 32-bit timers

- Built-in 1 Independent watchdog (IWDG)

- Built-in 1 set of window watchdog (WWDG)

- GPIO

- Supports seven GPIO ports and can be used as the main control IC

- Each GPIO port can be configured with the interrupt function

- Some GPIOs support direct communication of wide-voltage 5V level signals without

external level conversion

#### Software development support

- provide complete software development kit, application example and speech development platform online production firmware, and other functions, for details, please visit: https://aiplatform.chipintelli.com

#### ■ Firmware burning and protection

- Supports UART upgrade and firmware protection

#### ■ EMC and ESD

- Good EMC design, support FCC standards

- Internal ESD enhanced design, can pass 4KV contact discharge test

#### ROHS and REACH

- The use of environmentally friendly materials to support ROHS and REACH testing

#### Package and operating temperature range

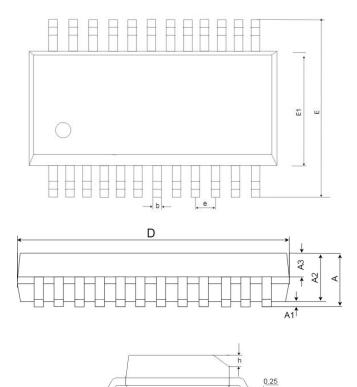

- Package form: TSSOP24, the size is 7.8mm long, 6.4mm wide, 1.2mm high

- Working environment temperature: -40°C to 85°C

# 2 Pin Diagram and Function Description

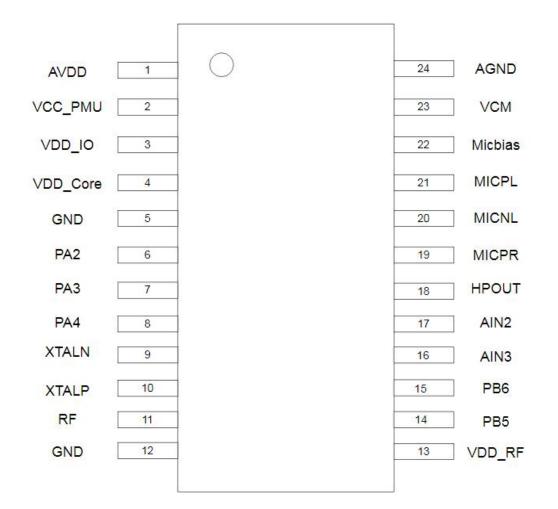

### 2.1 Pin Diagram

### 2.2 Pin descriptions

| Pin<br>numbe<br>r | Pin<br>Name | Typ<br>e | IO 5V<br>withsta<br>nd<br>voltage | IO<br>Power-on<br>Default<br>status | Pin reuse and function description |

|-------------------|-------------|----------|-----------------------------------|-------------------------------------|------------------------------------|

|-------------------|-------------|----------|-----------------------------------|-------------------------------------|------------------------------------|

#### Click to go to the Chipintelli official website

CI2312 Datasheet

|          |              |        | nek to go to t | ne Chipintelli o | GIZSTZ Datasnee                                                                                                                                                                                                                                                                                                                                                   |

|----------|--------------|--------|----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | AVDD         | Р      | -              | -                | The 3.3V analog LDO output pin is<br>also an analog power supply input pin<br>with an external 4.7uF capacitor.                                                                                                                                                                                                                                                   |

| 2        | VIN5V        | Р      | -              | -                | VIN5V is the PMU power input pin.<br>The normal input voltage ranges from<br>3.6V to 5.5V. A 4.7uf input capacitor<br>is externally connected. The<br>maximum input voltage of this pin is<br>6.5V. Please note that this pin<br>requires the addition of overvoltage<br>and surge protection, such as TVS<br>and 4.7 ohm resistance, to prevent<br>surge impact. |

| 3        | VDD33        | Р      | -              | -                | 3.3V LDO output pin, external 4.7uF capacitor                                                                                                                                                                                                                                                                                                                     |

| 4        | VDD11        | Р      | -              | -                | The 1.1V LDO output pin is also the core power supply input pin with 4.7uF capacitor                                                                                                                                                                                                                                                                              |

| 5        | GND          | Р      | -              | -                | Ground                                                                                                                                                                                                                                                                                                                                                            |

| 6        | PA2          | ΙΟ     | V              | IN, T+D          | <ol> <li>GPIO PA2 (Default power-on status)</li> <li>IIS_SDI</li> <li>IIC_SDA</li> <li>UART1_TX</li> <li>PWM0</li> </ol>                                                                                                                                                                                                                                          |

| 7        | PA3          | ΙΟ     | V              | IN, T+D          | <ol> <li>GPIO PA3 (Default power-on status)</li> <li>IIS_LRCLK</li> <li>IIC_SCL</li> <li>UART1_RX1</li> <li>PWM1</li> </ol>                                                                                                                                                                                                                                       |

| 8        | PA4          | Ю      | V              | IN, T+D          | <ol> <li>GPIO PA4 (Default power-on<br/>status) /PG_EN (Determine whether<br/>to program according to the level<br/>state during power-on, and start the<br/>programming function at high power<br/>times)</li> <li>IIS SDO</li> <li>PWM2</li> </ol>                                                                                                              |

| 9        | XTALN        | Ι      | -              | -                | Crystal oscillator pin negative                                                                                                                                                                                                                                                                                                                                   |

| 10       | XTALP        | Ι      | -              | -                | Crystal oscillator pin positive                                                                                                                                                                                                                                                                                                                                   |

| 11       | RF           | -<br>D | -              | -                | RF antenna                                                                                                                                                                                                                                                                                                                                                        |

| 12<br>13 | GND<br>VDDRF | P<br>P | -              | -                | Ground<br>1. VDD RF is the Bluetooth power<br>input pin. Input voltage is 3.3V. A<br>4.7uf input capacitor is externally<br>connected.                                                                                                                                                                                                                            |

| 14       | PB5          | Ю      | $\checkmark$   | IN, T+U          | <ol> <li>GPIO PB5 (Default power-on status)</li> <li>UART0 TX</li> <li>IIC_SDA</li> <li>PWM1</li> </ol>                                                                                                                                                                                                                                                           |

| 15       | PB6          | Ю      | $\checkmark$   | IN, T+U          | <ol> <li>GPIO PB6 (Default power-on status)</li> <li>UART0_RX</li> </ol>                                                                                                                                                                                                                                                                                          |

Click to go to the Chipintelli official website

**CI2312 Datasheet**

|    |        |    |   |         | 3. IIC_SCL                           |

|----|--------|----|---|---------|--------------------------------------|

|    |        |    |   |         | 4. PWM2                              |

|    |        |    |   |         | 1. Reserve (Default power-on status) |

|    |        |    |   |         | 2. GPIO PC3                          |

| 16 | AIN3   | IO | - | IN, T+U | 3. PWM1                              |

|    |        |    |   |         | 4. PDM_DAT                           |

|    |        |    |   |         | 5. SAR ADC input channel 3           |

|    |        |    |   |         | 1. Reserve (Default power-on status) |

|    |        |    |   |         | 2. GPIO PC4                          |

| 17 | AIN2   | IO | - | IN, T+U | 3. PWM0                              |

|    |        |    |   |         | 4. PDM_CLK                           |

|    |        |    |   |         | 5. SAR ADC input channel 2           |

| 18 | HPOUT  | 0  | - | -       | DAC output                           |

| 19 | MICPR  | Ι  | - | -       | Right Microphone P input             |

| 20 | MICNL  | Ι  | - | -       | Left Microphone N input              |

| 21 | MICPL  | Ι  | - | -       | Left Microphone P input              |

| 22 | MICBIA |    |   |         | Mismonhana biga autout               |

| 22 | S      | 0  | - | -       | Microphone bias output               |

| 23 | VCM    | 0  | - | -       | VCM Output                           |

| 24 | AGND   | Р  | - | -       | Analog ground                        |

Symbol definition:

I input

O output

IO bidirectional

P Power and ground

T+D triplet pull-down

T+U three-state pull-up

OUT Indicates the default power-on output

IN Specifies the default value for power-on

All I/O drive capabilities can be configured, and pull-down resistors can be configured.

### 2.3 Alternate functions

| Pin<br>Name | Function<br>1 | Function2     | Function 3 | Function4    | Function5   | Analog<br>Function | Specific<br>Functio<br>n |

|-------------|---------------|---------------|------------|--------------|-------------|--------------------|--------------------------|

| PA2         | PA2           | IIS_SDI       | IIC_SDA    | UART1_T<br>X | PWM0        | -                  |                          |

| PA3         | PA3           | IIS_LRCL<br>K | IIC_SCL    | UART1_R<br>X | PWM1        | -                  |                          |

| PA4         | PA4           | IIS_SDO       | -          | -            | PWM2        | -                  | PG EN<br>Note1           |

| PB5         | PB5           | UART0 T<br>X  | IIC_SDA    | PWM1         | -           | -                  |                          |

| PB6         | PB6           | UART0_R<br>X  | IIC_SCL    | PWM2         | -           | -                  |                          |

| AIN2        | -             | PC4           | -          | PWM0         | PDM_CL<br>K | AIN2               |                          |

| AIN3        | -             | PC3           | -          | PWM1         | PDM DA<br>T | AIN3               |                          |

Table 2-2 Alternate functions

Note1: P12-pa4 (PG\_EN) of the chip is automatically pull-up by default. When the power-on is judged to be high, the chip automatically enters the upgrade mode when an upgrade signal is detected on UART0 during power-on. At this time, the matching upgrade tool can be used to program the Nor Flash inside the chip. If no upgrade signal is detected on UART0, it will enter the normal working mode.

# **3** Electrical Characteristics

| Symbol            | Description                                                                                                                                                                     | Min.          | Typical | Max.          | Unit |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------|---------------|------|

| VIN5V             | PMU input pin voltage generally<br>5V                                                                                                                                           | 3.6           | 5       | 5.5           | V    |

| AVDD              | Analog and Codec supply voltages                                                                                                                                                | 2.97          | 3.3     | 3.63          | V    |

| VDD33             | Chip IO supply voltage                                                                                                                                                          | 2.97          | 3.3     | 3.63          | V    |

| VDD11             | Chip core power supply voltage                                                                                                                                                  | 0.99          | 1.1     | 1.22          | V    |

| VDDRF             | Bluetooth supply voltage                                                                                                                                                        | 1.9           | 3.3     | 3.6           | V    |

| $V_{\mathrm{IH}}$ | Output high voltage, $3.0V \le VDD33 \le 3.6V$                                                                                                                                  | 0.7×VDD<br>33 | -       | -             | V    |

| V <sub>IL</sub>   | Output low voltage, $3.0V \le VDD33$<br>$\le 3.6V$                                                                                                                              | -             | -       | 0.3×VDD3<br>3 | V    |

| V <sub>OL</sub>   | Output low voltage @IOL = 12mA                                                                                                                                                  | -             | -       | 0.4           | V    |

| V <sub>OH</sub>   | Output high voltage @IOH = 20mA                                                                                                                                                 | 2.4           | -       | -             | V    |

| I5VIO             | IO (5V withstand voltage) Output<br>3.3V drive current                                                                                                                          | 5             | -       | 23            | mA   |

| I33VIO            | IO (3.3V withstand voltage) Output<br>3.3V drive current                                                                                                                        | 12            | -       | 26            | mA   |

| ΣIVDD             | Sum of all IO currents of the chip                                                                                                                                              | -             | -       | 180           | mA   |

| Pde               | 5V power supply, chip 1.1V<br>external DC-DC chip power supply,<br>the total power consumption of $5V$<br>input during normal recognition<br>(ambient temperature TA = $25$ °C) | 70            | -       | 150           | mW   |

| Pdi               | 5V is used to power the chip, the<br>chip uses internal PMU, and the<br>total power consumption of 5V<br>input during normal recognition<br>(ambient temperature TA = 25 °C)    | 145           | -       | 250           | mW   |

| TA<br>Note1       | The chip uses an external crystal<br>oscillator to adapt to the operating<br>environment temperature                                                                            | -40           | -       | +85           | °C   |

| T <sub>ST</sub>   | The chip stores ambient temperature                                                                                                                                             | -55           | -       | +150          | °C   |

Table 3-1 Lists the electrical characteristics

Note2: 16MHz 10ppm crystal oscillator is required for chip operation.

# **4** Wireless characteristics

| Parameter             | Symbol  | Conditions         | MIN  | ТҮР | MAX  | UNIT |

|-----------------------|---------|--------------------|------|-----|------|------|

| Current in power down | Ipd     | Register retention | -    | 2   | -    | uA   |

| Current in standby    | Istb    | Crystal on         | -    | 40  | -    | uA   |

| Current in TX 0dBm    | Itx     | PA under 0dBm      | -    | 15  | -    | mA   |

| Current in RX 2Mbps   | Irx     | RX mode            | -    | 17  | -    | mA   |

| Operation frequency   | Freq    | -                  | 2400 | -   | 2525 | MHz  |

| PLL frequency step    | Delta F | -                  | -    | -   | 1    | MHz  |

| Freq deviation@1Mbps  | Df      | -                  | -    | -   | 250  | KHz  |

| Freq deviation@2Mbps  | Df      | -                  | -    | -   | 320  | KHz  |

The above power consumption data is measured when VDDRF is equal to 3.3V

# **5** Packaging Information

0,

| COMMON DIMENSIONS |                  |      |      |  |  |  |  |

|-------------------|------------------|------|------|--|--|--|--|

| SYMBOL            | UNIT: MILLIMETER |      |      |  |  |  |  |

|                   | MIN              | NOM  | MAX  |  |  |  |  |

| А                 | -                | _    | 1.2  |  |  |  |  |

| A1                | 0.05             | -    | 0.15 |  |  |  |  |

| A2                | 0.8              | 1.00 | 1.05 |  |  |  |  |

| b                 | 0.19             | 0.30 |      |  |  |  |  |

| с                 | 0.09             | _    | 0.20 |  |  |  |  |

| D                 | 7.70             | 7.90 |      |  |  |  |  |

| Е                 | 4.30             | 4.50 |      |  |  |  |  |

| E1                | 6.20             | 6.40 | 6.60 |  |  |  |  |

| e                 | 0.65BSC          |      |      |  |  |  |  |

| L                 | 0.45             | 0.60 | 0.75 |  |  |  |  |

| L1                | 1.00REF          |      |      |  |  |  |  |

| θ                 | 0 _ 8°           |      |      |  |  |  |  |

#### COMMON DIMENSIONS

## 6 Order Information

| Orderable<br>Device | Flash  | Status | Package<br>Type | Pins | Package<br>Qty | Eco Plan        | MSL<br>Peak Temp      | Op<br>Temp<br>(°C) |

|---------------------|--------|--------|-----------------|------|----------------|-----------------|-----------------------|--------------------|

| CI2312              | 2MByte | MP     | TSSOP24/Tube    | 24   | 50             | RoHS &<br>Green | Level-3<br>260C-UNLIM | -40 to 85          |

- Chipintelli reserves the right to change the instruction without further notice. Customers should obtain the latest version before placing an order, and verify that the relevant information is complete and up-to-date.

- Under specific conditions, any semiconductor product has a certain possibility of failure or failure. The buyer has the responsibility to comply with safety standards and take safety measures when using the product for system design and manufacturing, to avoid potential failure risk which may cause personal injury or property loss.

- Product improvement is endless. Chipintelli will provide customers with better products wholeheartedly!