硬件设计¶

CI1316X芯片需少量外围仅器件,即可开发出支持各类语音应用的终端产品方案。该芯片支持单麦克风差分或单端输入。应用方案设计可根据方案所需的功能、功耗和成本等需求因素,选择适合的电路设计方案。

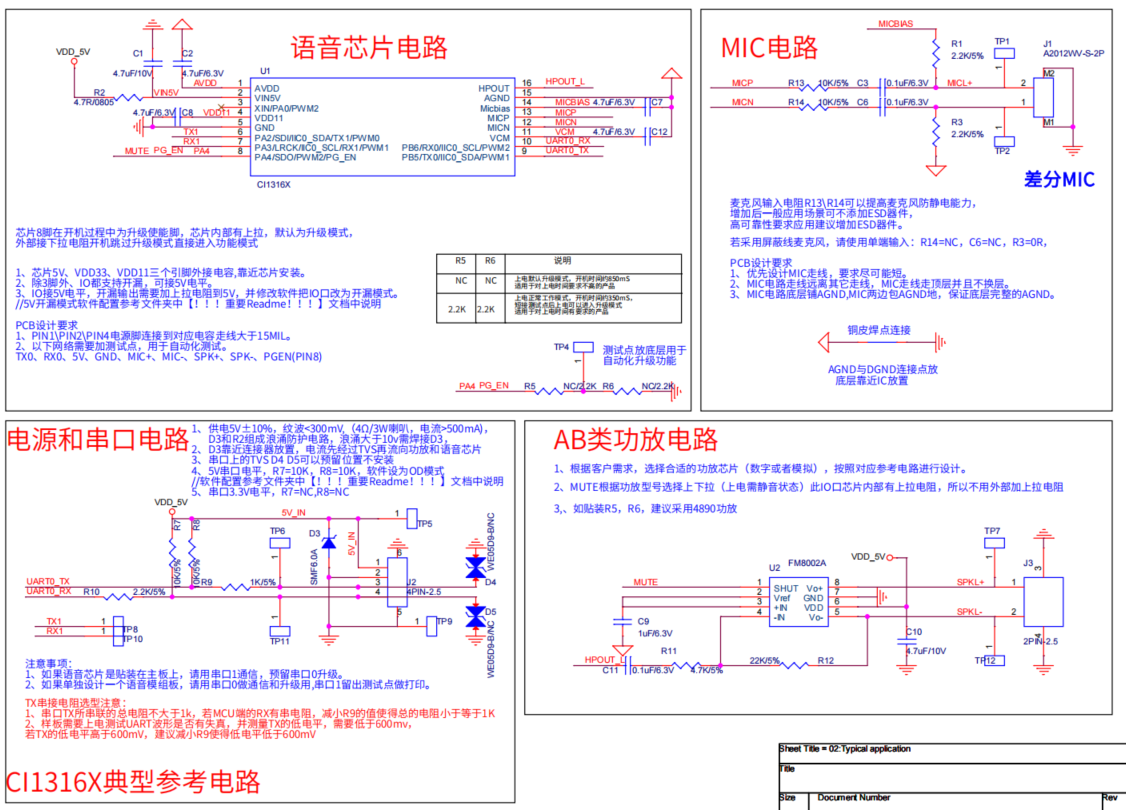

以下以CI13162的典型应用方案为例,介绍应用方案设计的要点和注意事项:

应用参考电路图¶

上图为包括CI13162在内的CI1316X系列芯片,单麦克风差分输入和功放输出的典型应用方案的参考设计电路图,该设计不局限于匹配某个具体的终端产品。应用方案的设计应基于适配上位机终端产品的原则,根据终端产品的功能和性能需求,前往启英泰伦文档中心和AI平台下载参考原理图和参考PCB图。文档中心链接:https://document.chipintelli.com/。

应用方案设计时若需预留板级升级功能,可以将UART0引脚以插座或测试点的方式引出,以便于PCB板贴片完成后通过UART0烧写或升级固件。

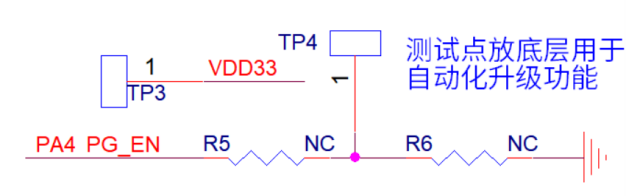

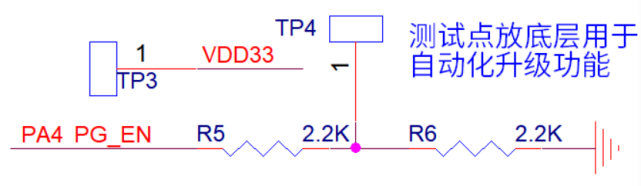

CI13162的PA4(PG_EN)管脚在芯片内部预置有3.3V上拉电阻,上电时系统将检测该引脚是否被置为3.3V高电平,若是高电平且检测UART0引脚有外部输入的升级信号,系统即进入升级模式。若该引脚外部接下拉电阻到地,芯片上电时可跳过升级模式检测环节直接进入正常启动模式,以实现系统的快速开机。若应用方案有快速开机需求,可将PA4引脚引出,并串接两个2.2KΩ的下拉电阻到地,两个2.2KΩ电阻之间预留一个测试点(具体实施方案请参照参考应用图原图或咨询我司的FAE),该设计状态下系统上电时为正常功能启动模式,开机时间可缩短为350ms左右。若此时需要在线升级,可通过两颗2.2KΩ电阻之间的测试点外供3.3V高电平,将PA4引脚电平拉高,即可通过UART0口升级。PG_EN两种工作模式如下表

| PG_EN外接电阻图示 | R5\R6安装情况 | PG_EN高低电平 | 开机时间 |

|---|---|---|---|

|

R5\R6都NC | 高电平,升级模式 | 850ms |

|

R5\R6贴2.2K | 低电平,工作模式 | 350ms |

CI13162支持差分麦克风输入或单端麦克风输入,推荐采用图H-1中的差分麦克风设计。低成本设计方案可采用单端麦克风输入设计,以减少麦克风输入线路上的器件,但该方式仅推荐用于麦克风输入线路长度小于20厘米的方案,否则麦克风输入线路太长将影响其抗干扰的能力,导致语音识别效果变差。

该典型应用方案的功放配置为AB类功放,推荐采用8002系列功放。若不需要语音播报功能,可去除该部分电路以降低方案成本。

若应用方案没有超低功耗要求,建议设计方案采用CI13162内部的PMU供电以降低成本。若应用方案有超低功耗要求,可采用外部DCDC电路给CI13162供电1.1V,以降低系统功耗。

CI13162的UART口均可支持5V电平通讯。上图中的UART0口是以3.3V通讯电平为例,应用方案若需外接5V通讯电平,在UART0的RX和TX引脚外围增加5V上拉电阻即可,无需配置电平转换电路。

PCB Layout设计¶

电源电路¶

电源走线¶

电源输入注意防护过压及浪涌防护,在5V输入设计TVS器件和4.7欧姆电阻,走线先经过TVS再经过电阻到芯片。电源走线直径依据实际电路电流大小而定,3.3V电源的走线线宽不小于15mil,1.1V电源的走线线宽不小于15mil。尽量使用覆铜方式走线,电源走线尽量短而粗,电源走线最窄处不低于8mil线宽,避免电源走线形成闭环线路。

电源退耦电容¶

电源退耦电容,布局时靠近对应的管脚。

静电防护要求¶

两层板设计时,尽量走线在TOP层,保持BOTTOM地平面的完整性。如设计有ESD器件,将ESD器件尽量靠近端子的引脚,提高防护效果。

应用其它注意事项¶

-

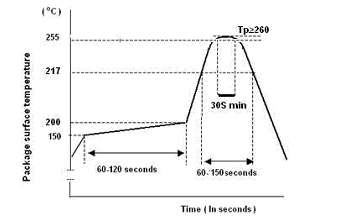

CI1316X采用无铅环保材料制造,SMT焊接时请按照无铅标准设置炉温和时间参数。一个SMT焊接的温度曲线如下图所示:

图H-2 芯片SMT焊接温度曲线

图H-2 芯片SMT焊接温度曲线 -

CI1316X的取用、搬运、生产加工等过程需注意采取防静电措施,其包装需采用防静电材料。

-

芯片的潮湿敏感度等级为MSL3级,使用前请按照MSL3级条件存储。如果开包装后存放时间超过MSL3级的要求,请在SMT焊接前先进行烘烤。