硬件设计¶

CI230X系列芯片外围仅需要少量器件就可以支持各类离在线语音应用。针对语音部分,该芯片可以支持双麦克风输入或单麦克风输入加AEC回声消除的方案。用户可以根据设计的应用方案功能、功耗和成本要求选择合适的电路,下面对该芯片一个单麦克风输入加AEC回声消除方案的应用参考电路图做具体描述。

应用参考电路图¶

上图为CI230X系列芯片一个支持单麦克风输入加AEC回声消除和功放输出的应用方案电路图。该芯片可以采用5V直接供电,用户可按照上图中对应的外围器件规格来进行设计。原理图设计时如果要考虑板级在线升级功能,可以将UART0引脚引出,以方便PCB板贴片完成后通过UART0对主芯片内部的Flash进行固件升级。芯片的PA4(PG_EN)引脚内部带上拉,上电默认为升级模式,开机后要检测外部UART0口发来的升级信号,如果有则直接启动升级。芯片默认的开机时间因为增加了升级模式的检测而延长,大概约850mS;如果用户对开机时间有很高的要求,可以将PA4脚引出,增加两个2.2K的下拉电阻到地,两个2.2KΩ电阻连接的中间增加一个测试点,此时芯片开机为正常模式,开机时间大概约350mS,可以缩短开机时间。如果此时要在线升级可以通过外部给两个2.2KΩ电阻连接的中间测试点供高电平,将PA4引脚拉高,再通过UART0升级。

该芯片方案可选用差分麦克风设计或单端麦克风设计,推荐采用上图中的差分麦克风设计。如果用户对成本有要求,可以将上图中麦克风部分修改为单端麦克风设计,可以比差分麦克风少使用一些被动器件,但该方式仅推荐应用在麦克风线长小于20厘米的场合中,否则会因为线太长,抗干扰效果不够,导致语音识别效果没有差分麦克风设计的方式好。上图中功放采用的是AB类的功放,推荐采用8002功放芯片,用户也可以按照方案的要求自行选择功放芯片,如果不需要功放功能时也可以去掉该部分电路以降低成本。用户如果不用AEC回声消除功能,也可以去掉该部分电路以降低成本。

用户如果对方案的功耗没有特殊要求时,建议直接采用芯片内部的PMU供电,如果有功耗要求,可以采用增加外部DCDC芯片给芯片1.1V供电,以降低功耗。芯片的UART口均支持5V通信,上图中的UART0口是接的3.3V信号,如果要接5V,在UART0的RX和TX管脚外围增加连接到5V的上拉电阻即可,不用额外增加电压转换电路。

该芯片VDDA33和VDD33W引脚为Wi-Fi供电输入脚,上图中采用的是DCDC供电,推荐采用RY3408 DCDC芯片,用户也可以按照方案的要求自行选择DCDC芯片。DCDC芯片电流驱动能力须大于1A,且仅为Wi-Fi供电以确保Wi-Fi性能稳定。

该芯片RSTn和EN引脚均可用于复位Wi-Fi功能,复位时推荐采用上图中的EN引脚。该芯片PE2和PE3引脚默认为Wi-Fi固件下载串口,PE9引脚默认为Wi-Fi固件下载使能口。下载Wi-Fi固件时,需要将PE2和PE3引脚接至串口,将PE9引脚拉低到地,再给芯片上电,使芯片进入下载模式,然后可通过我司提供的下载软件下载固件。

该芯片外围采用的晶体规格为40Mhz CL=12pF 10ppm,需要在XIN、XOUT引脚上外接4.7pF电容。该晶体的参数规格不可随意更换,请用户严格按照原理图中的设计执行。

该芯片RFIO引脚为天线脚,上图中预留了一级T型匹配网络电路。用户可根据PCB实际叠层情况以及天线规格,预留芯片端匹配网络和天线端匹配网络电路。不同的PCB叠层、天线规格以及PCBA装配的不同环境,都需要单独调试匹配网络电路,以确保射频性能。

PCB Layout设计¶

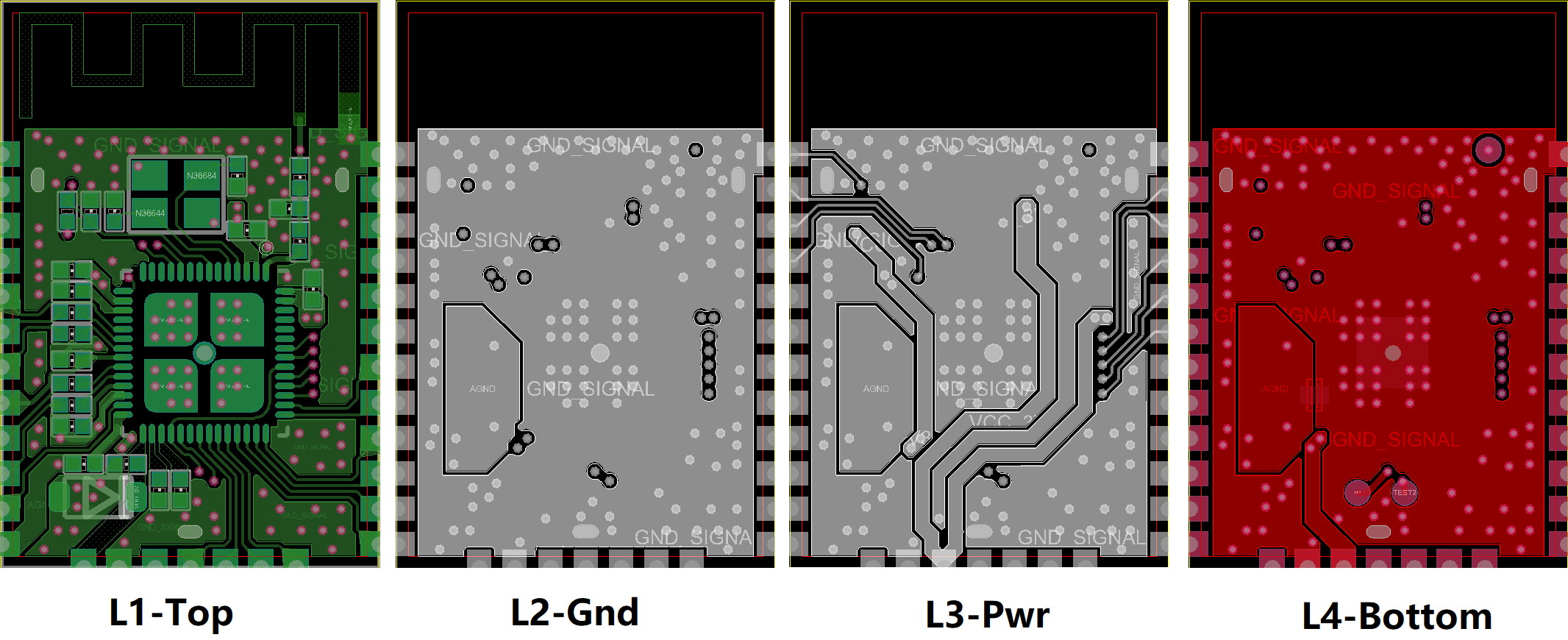

推荐采用4层板设计,第一层放置器件,第二层保持完整的地平面,第三层走电源线及其他走线,第四层保持完整的地平面。如图H-2所示:

电源电路¶

-

芯片参考电路 VIN_5V 为 5V 供电输入脚,纹波要求 < 100mV。5V 为典型供电电压,输入超过 5.5V 电压有概率损坏电路。芯片电路在播音状态下 5V 最大电流能达到 250mA(含外部 4Ω/3W 喇叭),按照两倍余量原则上需要为该电路提供一组驱动能力为 500mA 的电源供电。同时,须串联一颗 4.7R 0805封装电阻至该电路 VIN_5V 脚,与该电路内部 TVS 组成浪涌防护电路,不可删除。

-

芯片参考电路 VDDA33 和 VDD33W 为 Wi-Fi 3.3V 供电输入脚,需单独供电。推荐采用 DCDC 供电,如 RY3408 DCDC 芯片,用户也可以按照方案的要求自行选择 DCDC 芯 片。DCDC 芯片电流驱动能力须 > 1A。同时pin2&pin3(VDDA33)、pin55&pin56(VDDA33)、pin16(VDD33W)推荐从电源入口星型走线至管脚,走线间用GND隔离。

-

若有 FCC/CE 等EMI认证测试要求,VIN_5V 及 VDD33 建议预留 100pF 接地电容,靠近芯片参考电路管脚放置。

-

若输入电源纹波较大,则须增加电解电容等其他纹波改善措施。

-

电源及地线走线尽量宽,建议 > 15mil。

射频电路¶

-

芯片匹配网络尽量靠近RFIO脚放置。

-

RF 走线须做50欧姆阻抗控制,顶层尽量保证RF走线周围的地完整性。

-

天线区域须保持铜皮镂空。

晶体电路¶

-

确保晶体周围良好的包地。

-

顶层晶体焊盘周围铜皮镂空,晶体GND脚直接通过过孔连接至第二层GND。

静电防护要求¶

尽量走线在TOP和第三层,保持第二层和BOTTOM地平面的完整性。如设计有ESD器件,将ESD器件尽量靠近插件的引脚,提高防护效果。

应用其它注意事项¶

- CI230X系列芯片方案推荐直接使用外接晶振(PA0、PA1外接12.288M晶体电路)。如果用户对成本有较高要求,但对芯片主频大小和精度、工作环境温度范围无要求的,可以采用芯片内置的RC振荡器,但请注意芯片内置的RC振荡器因半导体技术原理,在高温和低温环境会产生一定的温漂,使用时请降低系统主频到220MHz以下。如果应用的工作环境温度需要-40到85℃,请采用外接晶振。

- 如果应用场景的工作温度范围在-10到70℃,且仅和上位机进行低速串口通信(波特率小于或等于115200bps),该类电路方案可以直接采用芯片内置的RC振荡器(上位机频偏 ≤ ±1.5%)。当上位机为免晶振设计时,需要尽量减小通讯误差。启英泰伦可提供串口波特率自适应方案,该方案需要在串口协议中增加一个握手指令,并且上位机保证在收到该握手指令的50ms内会按照协议要求回复。增加该自适应方案后,产品可以用于工作环境温度为-20到85℃的场景。

- 芯片集成了PMU管理单元,PMU包含多个LDO,分别给芯片提供3.3V和1.1V电压,外供5V电源纹波需小于300mV。如对射频性能及功耗要求高,建议外置电源芯片给VDDA33及VDD33W单独供电。

- 射频器件对晶体频偏敏感,如产品工作环境恶劣,建议选择宽温晶体。

- RFIO引脚须预留匹配网络,且走线须做阻抗匹配。如走线过长,建议在靠近天线的地方也预留匹配网络。

- 如产品有播报音频的需求,AGND和HPOUTL引脚要以差分走线的方式连接到功放,避免音频被干扰及产生异响。

- 芯片采用无铅环保工艺制造,SMT焊接时请按照无铅标准设置炉温和时间等参数。

- 芯片取用、包装时需注意静电影响,建议采用抗静电材料隔离。