接口描述¶

通用输入输出(GPIO)¶

简介¶

GPIO(通用IO接口)是一种通用的输入输出端口,允许设备与外围硬件进行电平信号交互,其既可以作为输入接收外部信号,也可以作为输出控制外围硬件。

特性¶

CI13082V支持多个可编程的输入/输出管脚(可由软件单独配置),每个GPIO端口都有相应的控制寄存器和配置寄存器,可单独打开或关闭每个GPIO管脚,实现对外围硬件的精准控制和状态监测。CI13082V芯片支持2组GPIO(GPIO1、GPIO2),其中GPIO1对应的是芯片PB口,GPIO2对应的是芯片PC口。每组GPIO管脚分配请查看2.2管脚描述部分。

CI13082V提供IO输入输出状态查询接口、中断屏蔽接口、中断屏蔽查询接口、中断清除接口、中断状态查询接口、中断触发方式配置接口(可配置为:低电平触发、高电平触发、上升沿触发、下降沿触发、双边沿触发)等,以满足不同的应用场景和需求。

通用异步收发传输器(UART)¶

简介¶

UART是一种通用异步串行通信数据接口,实现两个设备之间数据的接收和发送,支持全双工通讯。接收端和发送端之间没有共享时钟信号,为保障通信可靠性,通讯的两个设备需要设置相同的波特率和数据帧格式。

CI13082V支持1个UART控制器:UART0。

特性¶

- 支持标准的UART协议,数据帧格式由起始位、数据位(长度可配置)、奇偶校验位(可选)和停止位(宽度可配置)四部分组成,支持波特率可配置。

- 总线处于空闲状态时,信号线为高电平状态。

- 起始位:用于标识传输数据帧的开始,每个数据帧以发送端输出一个比特宽度的低电平开始,通知接收端数据传输已启动;

- 数据位:传输的数据长度通过UART_LCR寄存器可配置为5~8位,常用8位,位传输顺序为低位优先,先发送最低位LSB最后发送最高位MSB;

- 奇偶校验位:通过UART_LCR寄存器配置是否开启奇偶校验功能,通过UART_LCR寄存器配置奇校验或偶校验。奇偶校验功能开启状态、数据位传输完成后,可通过奇/偶校验检测数据传输是否错误;

- 停止位:用于标识传输数据帧的结束,每个数据帧以高电平结束,长度通过UART_LCR寄存器可配置为1、1.5、2位;

时序图¶

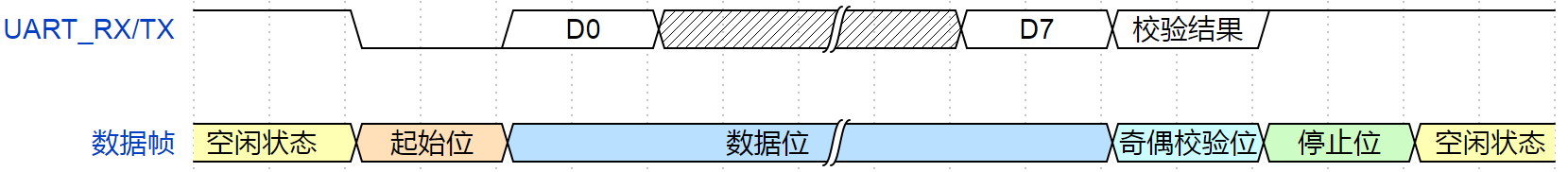

UART数据传输1个数据帧(8位数据位、奇偶校验位、1bit停止位)的时序图如下:

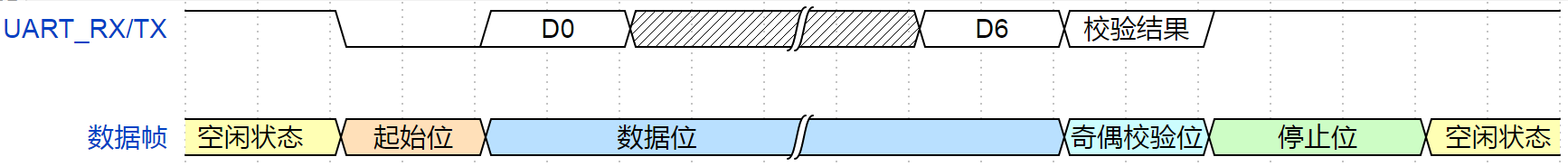

UART数据传输1个数据帧(起始位、7位数据位、奇偶校验位、1.5bit停止位)的时序图如下:

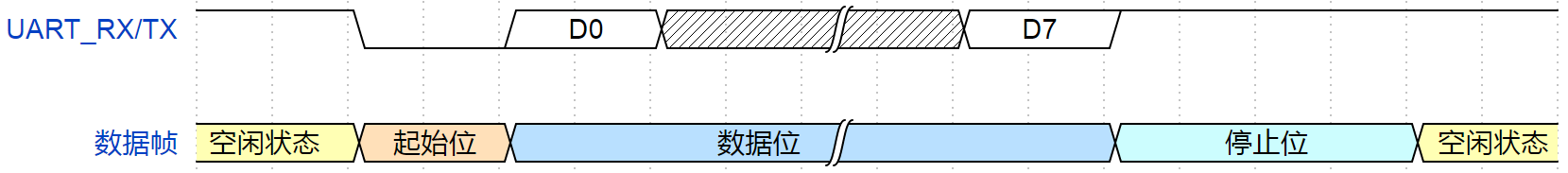

UART数据传输1个数据帧(起始位、8位数据位、无奇偶校验位、2bit停止位)的时序图如下:

UART波特率设置越高,数据传输速度越快,但也会增加干扰和误码率。在设置波特率时,需要考虑通信双方串口硬件是否支持该波特率。若波特率设置过高,可能会导致数据传输不稳定。

支持最大3Mbps波特率,波特率可通过UART_I_BRD和UART_F_BRD寄存器配置。

脉冲宽度调制输出(PWM)¶

简介¶

PWM(Pulse Width Modulation)是一种通过调节数字脉冲的占空比(高电平时间占整个周期的比例)来等效模拟信号电平的技术,广泛应用于电机控制、电源管理、LED调光等领域。

CI13082V具有4个专用PWM,每个PWM输出信号的频率通过TIMER_SC寄存器进行配置,每个PWM输出信号的占空比通过TIMER_SPWMC寄存器进行配置,不支持100%占空比(常高),若需使用100%占空比,通过配置GPIO来实现。

特性¶

- 计数时钟分频,支持1、2、4、16分频,通过TIMER_CFG寄存器进行配置;

- 支持两个32位递减计数器;

- 可变占空比PWM脉冲宽度波形输出;

- 支持停止后输出电平极性通过TIMER_RESTART_MD寄存器配置;

通用定时器(TIMER)¶

简介¶

TIMER(通用定时器)是一个基于可配置分频器和多种计数方式32位递减计数器,在计数值达到0时触发一个定时事件,常用于在指定的时间间隔内反复触发指定窗口的定时器事件,可作为周期性中断发生器、事件计数器使用。CI13082V具有2个相同的专用TIMER:TIMER0~TIMER1,支持TIMER级联。

特性¶

- 支持三种计数模式,通过TIMER_CFG寄存器进行配置:单周期计数模式、自动重装载计数模式、自由运行计数模式; 单周期计数模式:定时器仅计数一个计数周期; 自动重装载计数模式:计数器在每个计数结束时重新初始化; 自由运行计数模式:计数值在每次计数结束时从0xFFFFFFFF循环到0x00000000;

- 计数时钟分频,支持1、2、4、16分频,通过TIMER_CFG寄存器进行配置;

- 32位递减计数器,可读取计数器的实时值,通过TIMER_CC寄存器进行读取;

- 支持级联模式配置,通过TIMER_CFG0寄存器进行配置;

- 支持计数完成上报中断;

集成电路总线(IIC)¶

简介¶

IIC是一种双向双线同步串行总线,包括SDA(串行数据线)和SCL(串行时钟线),SDA和SCL管脚均为开漏输出。IIC总线通常用于单个或多个主设备和单个或多个从设备之间通信,每个连接到总线上的设备都有一个唯一的地址,同一时刻仅允许有一个master主设备发起请求访问slave从设备。

CI13082V支持1个IIC,其数据帧格式通常由起始信号、地址信号、应答信号、数据信号和停止信号五部分组成,支持标准传输速率100kbit/s和快速传输速率400kbit/s两种模式。

特性说明¶

- SDA:串行数据线,双向I/O线;

- SCL:串行时钟线,由master提供;

- 支持master和slave模式可寄存器配置;

- master:作为master主设备时启动总线传输数据,并产生时钟;

- slave:作为slave从设备时被寻址的从设备,具有唯一地址;

- 起始信号:SCL为高电平时,SDA从高电平跳变至低电平,表示传输开始;

- 地址信号:支持7位寻址模式,包含7bit地址位和1bit读写位;

- 应答信号:ACK接收成功,NACK接受失败或传输结束;

- 数据信号:按Byte传输,先发送最高位MSB最后发送最低位LSB;

- 停止信号:SCL为高电平时,SDA从低电平跳变至高电平,表示传输结束;

- 总线传输速率可配置为标准-100kbit/s和快速-400kbit/s;

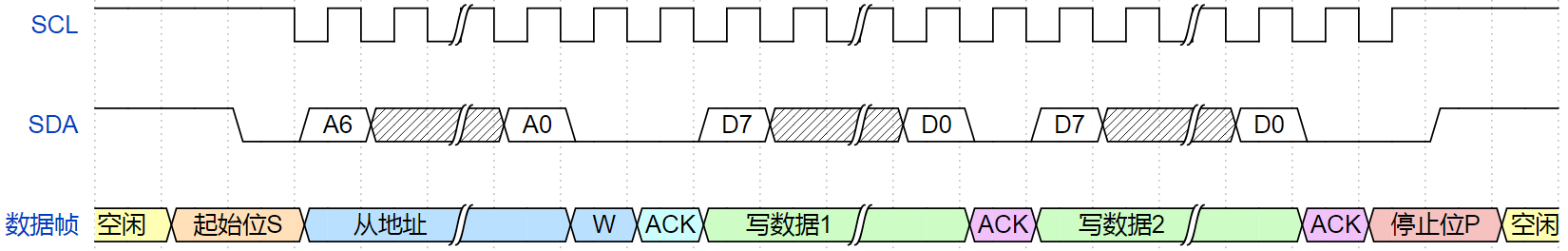

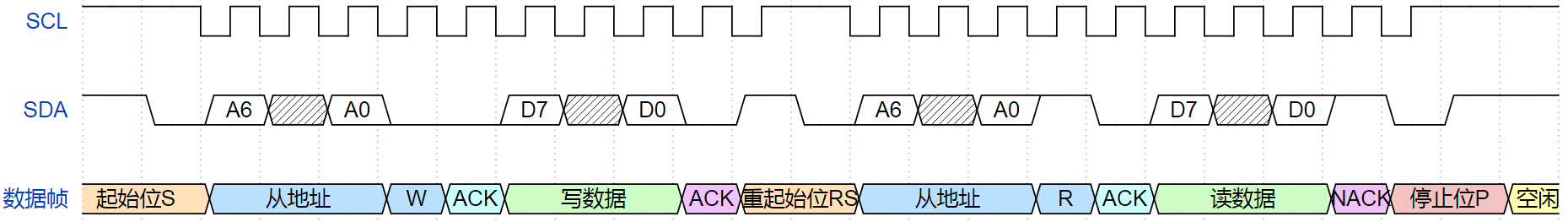

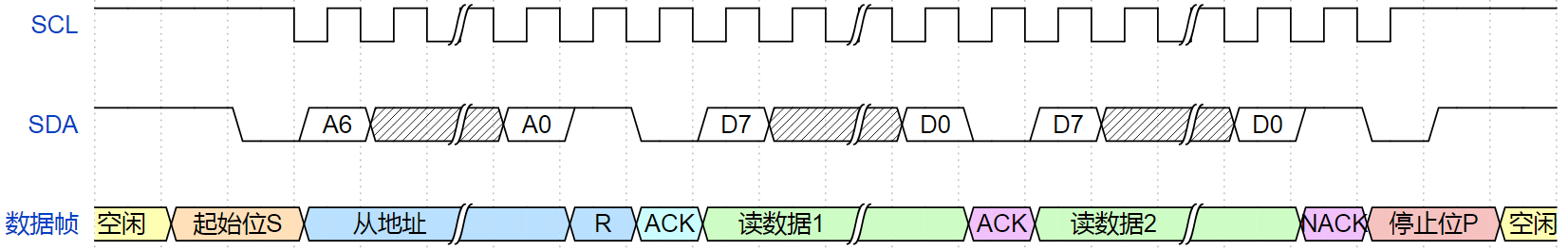

时序图¶

主设备通过产生Start起始条件来启动通信:在SCL为高电平时将SDA拉低,并通过SCL发送8个时钟脉冲用于传输1个Byte,该Byte包含7Bit地址位和一Bit读/写位。若从设备的地址与传输的7Bit地址匹配,则产生应答信号。主设备和从设备可根据读/写位判断是发送还是接收数据,并根据应答位的逻辑电平判断是否结束数据传输。在数据传输过程中,SDA仅在SCL为低时发生变化。一旦完成通信,主设备发送STOP停止条件来结束通信:在SCL为高电平时将SDA拉高。

独立看门狗(IWDG)¶

简介¶

IWDG是一种硬件定时电路,主要用于监测系统由于工作异常而引发的故障并从故障中进行恢复。

特性¶

CI13082V支持1个IWDG模块,IWDG是基于一个32位递减计数器,计数器从装载值开始递减,计数值计数到0时,产生超时中断,计数器重新加载装载值,计数值再次计数到0时,若超时中断未被清除,则IWDG将产生复位请求。

可通过SYS_RESET_CFG寄存器配置复位域的范围。

多媒体音频编解码器(CODEC)¶

简介¶

CI13082V内置高性能低功耗音频CODEC,支持一路ADC、一路DAC,MIC输入的模拟信号经MIC增益,再经PGA放大。此PGA可通过CODEC本身的ALC控制,PGA之后,还可通过数字增益进行放大。

特性¶

- DAC支持最多24bit,SNR可达90dB;

- ADC支持最多24bit,SNR可达90dB;

- 支持单端、差分的MIC输入和line-in输入;

- 支持ALC自动增益控制;

- 采样率支持:8k/12k/16k/24k/32k/44.1k/48k;

增强型脉冲宽度调制输出(EPWM)¶

简介¶

EPWM(增强型脉冲宽度调制输出)是一种比普通PWM更为复杂的脉冲宽度调制技术,具有更多功能和配置选项。它能够实现反向、斩波、低电平或高电平指定相位等特殊功能,广泛应用于工业及消费类电子领域电源控制器件,例如电机控制、开关电源等。

每个EPWM由2路PWM输出组成,分别为引脚PWMN和PWMP,且这一对PWM输出可单独当作普通PWM使用,或者互补PWM波输出,或者自定义的PWM输出。

特性¶

- 一个频率可控的16-bit计数器;

- 支持外部或软件通过TBCTL寄存器配置计数器的开始或结束;

- 支持一对多种模式的PWM输出:中心对称PWM输出;边沿对称PWM输出;边沿非对称PWM输出;

- 支持初始相位通过TBPHS寄存器配置;

- 16-bit死区时间,支持上升沿或下降沿的延迟时间通过DBRED或DBFED寄存器配置;

- 外设刹车命令到来时,PWM输出通过TZSEL寄存器可配置为高电平、低电平、高阻态;

配置值说明¶

EPWM的核心配置参数包括TBPRD、ZERO、CMPA和CMPB。其中TBPRD定义了PWM波的周期长度,CMPA和CMPB则用于设置占空比。通过配置这些参数,可控制PWM波的频率和占空比。

- TBPRD:计数周期值(>0),配置宽度最大为16位,通过AQCTLA或AQCTLB寄存器配置计数到TBPRD值时产生拉高、拉低或不变等动作;

- ZERO:计数周期值(=0),通过AQCTLA或AQCTLB寄存器配置计数到ZERO值时产生拉高、拉低或不变等动作;

- CMPA:计数比较值A,配置宽度最大为16位,通过AQCTLA或AQCTLB寄存器配置计数到CMPA值时产生拉高、拉低或不变等动作;

- CMPB:计数比较值B,配置宽度最大为16位,通过AQCTLA或AQCTLB寄存器配置计数到CMPB值时产生拉高、拉低或不变等动作;

计数模式¶

EPWM支持三种计数模式:递增模式、递减模式和增减模式。不同的计数模式适用于不同的应用场景。

- 递增模式:计数器每个周期均是从0递增到TBPRD。1个TBPRD周期就能输出1周期PWM,支持通过TBCTR寄存器配置;

- 递减模式:计数器每个周期均是从TBPRD递减到0。1个TBPRD周期就能输出1周期PWM,支持通过TBCTR寄存器配置;

- 增减模式:计数器在奇数周期从0向TBPRD递增,在偶数周期从TBPRD递减到0。2个TBPRD周期就能输出1周期PWM,支持通过TBCTR寄存器配置;

使用方法¶

EPWM可通过配置输出多种不同的波形,例如50%占空比PWM波、低电平占空比PWM波等。若要得到所需波形,首先需要配置TBPRD、CMPA、CMPB的值,并指定其计数模式,再配置计数器计数到TBPRD、ZERO、CMPA、CMPB值时分别产生什么动作,最终就能输出所需的波形。在该过程中,允许配置CMPA= CMPB,或者CMPA> CMPB,或者CMPA<CMPB。