Hardware Design¶

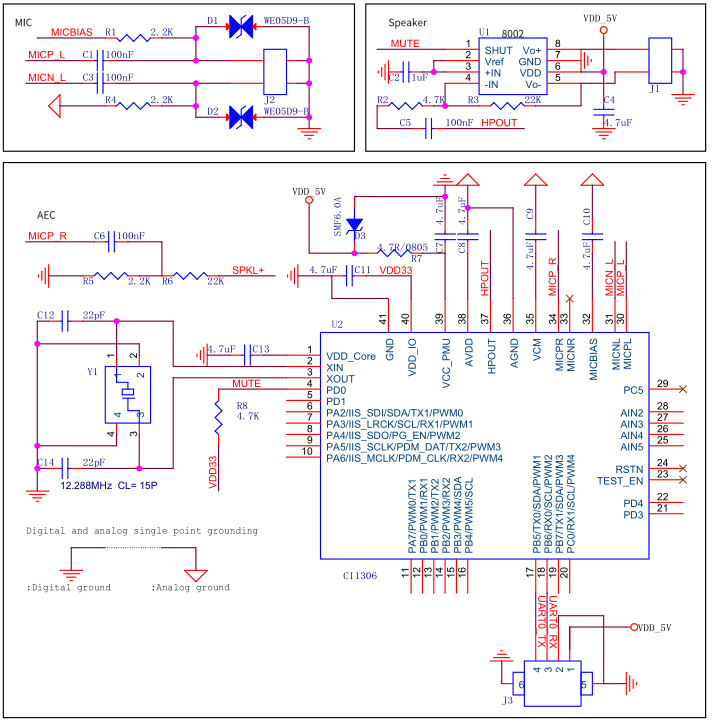

The CI1306 chip requires only a few external components to support various voice applications. For the audio part, the chip supports both dual microphone input and single microphone input with AEC (Acoustic Echo Cancellation). Users can select appropriate circuits based on design requirements for functionality, power consumption, and cost. Below is a detailed description of the application reference circuit for single microphone input with AEC.

Application Reference Circuit Diagram¶

The application reference circuit diagram is shown in Figure H-1: * CI1306 application solution supports single microphone input, AEC, and power amplifier output.

The chip can use 5V direct power supply, and users can design according to the corresponding peripheral device specifications in the figure above.

If the board-level online upgrade function is to be considered during schematic design, the UART0 pin can be led out to facilitate Firmware Update of the flash in the main chip through UART0 after PCB board placement is completed. The PA4 (PG_EN) pin of the chip is internally pulled up. Power-on defaults to upgrade mode. After power-on, the upgrade signal sent from the external UART0 port should be detected. If there is one, the upgrade should be started directly. Extended by adding detection of upgrade mode, the default boot time of the chip is about 850mS; If the user has high requirements for boot time, the PA4 pin can be led out, two 2.2K Ω pull-down resistors can be added to ground, and a test point can be added between the two 2.2K Ω resistors. At this time, the chip is powered on in normal mode, and the boot time is about 350mS, which can shorten the boot time. If you want to upgrade online at this time, you can externally supply high level to the intermediate test points connected by two 2.2K Ω resistors, pull up the PA4 pin, and then upgrade through UART0.

Application with this chip can select differential microphone design or single-ended microphone design, and the differential microphone design in the above figure is recommended. If the user has requirements for cost, the microphone part in the above figure can be modified to a single-ended microphone design, which can use fewer passive devices than the differential microphone. However, this method is only recommended for applications where the microphone line length is less than 20 cm, otherwise the speech recognition effect will not be as good as the differential microphone design because the line length is too long and the anti-interference effect is not enough. The power amplifier shown in the figure above is a Class AB amplifier, with the 8002 power amplifier chip recommended in the diagram. Users may select alternative power amplifier chips based on their specific solution requirements. If the power amplifier function is not required, this circuit section can be omitted to reduce costs. For applications requiring AEC, users can utilize a microphone input channel to connect the AEC analog signal input.

If the user has no special requirements for the power consumption of the solution, it is recommended to directly use the PMU inside the chip for power supply. If there is a power consumption requirement, the external DCDC chip can be added to power the chip 1.1V to reduce the power consumption. All UART ports of the chip support 5V communication. The UART0 port in the above figure is a 3.3V signal. If 5V is to be connected, add a pull-up resistor connected to 5V around the RX and TX pins of UART0. No additional voltage conversion circuit is required.

Chipintelli offers multiple reference schematics for common applications. For development, select the most suitable schematic based on product requirements, system characteristics, and application scenarios. As Chipintelli is unable to master all product systems and application knowledge, customers or solution partners are expected to fully test and verify product functional performance (including the matching of voice chips and modules with product systems) in combination with product systems and application scenarios before mass production. If there are unclear and uncertain problems during the design modification process, please contact Chipintelli FAE engineer for full communication. Users can refer to the following documents:

| Solution | Solution function | Solution application scenario | Document center link |

|---|---|---|---|

| Typical solution | Single microphone differential microphone input with echo cancellation function | Suitable for widely used products, products with broadcasting and echo cancellation | ☞Reference schematic for typical solution |

| Dual microphone AEC solution | Dual microphone differential microphone input with echo cancellation function | Products with dual microphone input and echo cancellation requirements | ☞Reference schematic of dual microphone AEC solution |

The schematic source document and PCB reference can be found in the ☞Chipintelli AI Speech Development Platform.

PCB Layout Design¶

Power Circuit¶

1. Power Wiring

Power input should include overvoltage and surge protection. For 5V input, use TVS devices and 4.7 Ω resistors. Route the wiring through TVS first, then through resistors to the chip. Power supply trace widths should be at least 15mil for 3.3V and 1.2V supplies. Use copper clad traces where possible, keeping them short and thick. The narrowest power supply trace width must be at least 8mil to prevent closed loops

2. Power Decoupling Capacitor

The power decoupling capacitor is arranged close to the corresponding pin.

Electrostatic protection requirements¶

In the design of two-layer boards, try to route in the TOP layer to maintain the integrity of the BOTTOM ground plane. If ESD devices are designed, try to close the ESD devices to the pins of the plug-in to improve the protection effect.

Other Considerations for Application¶

- For CI1306, use an external crystal oscillator unless cost is critical and temperature range (-40 to 85°C) isn’t a concern. The built-in RC oscillator has temperature drift and requires system frequency < 220MHz. Use external crystal for applications operating between -40 to 85°C .

- For applications operating between -10°C to 70°C with low-speed serial communication (baud rate ≤ 115200bps), the internal RC oscillator may be used (with a frequency tolerance of ±1.5%). To minimize communication errors when using the internal oscillator, Chipintelli offers a baud rate adaptation solution. This requires implementing a handshake protocol where the host device must respond within 50ms of receiving the handshake command. With this adaptation, the operational temperature range can be extended to -20°C to 85°C.

- The chip’s PMU includes three LDOs for 3.3V and 1.1V supplies. No external power chip needed unless power consumption is critical. External 5V supply ripple must be < 300mV.

- The chip uses lead-free manufacturing. Follow lead-free SMT standards for temperature and time settings during welding.

- Handle and package chips with anti-static materials to prevent ESD damage.