CI13XX Low Power Solution Description¶

Overview¶

The CI13XX chip series supports low-power solutions, which require coordinated efforts from both hardware and software aspects. This document details the implementation methods from both hardware and software perspectives.

Low Power Hardware Solution¶

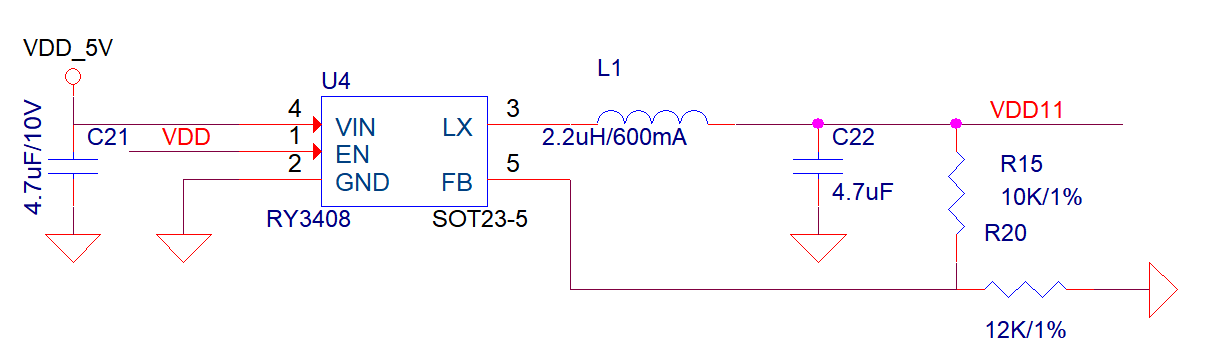

The hardware solution for the CI13XX series chips involves replacing the internal LDO (Low Dropout Regulator) power supply with a more efficient DCDC power supply. The DCDC power supply can achieve over 95% efficiency, compared to only about 30% efficiency for LDOs, thus effectively reducing power consumption. The DCDC power supply uses 5V input and 1.1V output connected to the VDD11 pin of the chip.

Reference diagram for the low-power hardware solution:

Figure 1 1.1V External DCDC Power Supply

Low Power Software Solution¶

For CI13XX series chips using DCDC power supply to reduce power consumption, the internal 1.1V LDO needs to be disabled in software. The configuration method is as follows:¶

#define USE_INNER_LDO3 0

USE_INNER_LDO3 to 0 in the SDK to disable the internal 1.1V LDO. Note: After making changes, clean and rebuild the project.

The low-power solution for CI13XX series chips also includes reducing the system’s main frequency. The configuration method is as follows:¶

define MAIN_FREQUENCY 180000000 //Main frequency in Hertz (Hz)